helldanger1

GForum VIP

- Entrou

- Ago 1, 2007

- Mensagens

- 29,629

- Gostos Recebidos

- 1

Com Ivy Bridge pouco mais de um mês afastado, Hiroshige Goto, contribuinte para o relógio do PC, estimou o layout de Ivy Bridge silício.

Como discutido na IEEE International Conference Circuitos de Estado Sólido , Siers Intel engenheiro Scott anunciou que haverá quatro diferentes modelos de matrizes Ivy Bridge. Além disso, Ivy Bridge irá transportar até 1,4 bilhões de transistores que decorrerá ao longo de uma área de 160 mm 2, que é cerca de 26 por cento menor do que a 216 milímetros comparável 2 morrem Sandy Bridge com 1,16 bilhões de transistores. Ivy Bridge é construído em 22 nm, que é o "carrapato" processo de Tock da Intel Tick Modelo .

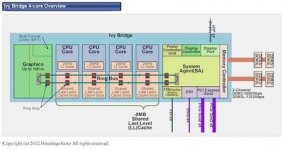

omar um olhar mais atento disposição da Ponte Ivy die estimado, o layout é similar no projeto atual geração Sandy Bridge. A matriz é composta por três seções gerais, 1), 2 núcleos de CPU) Agente de Sistema e 3) núcleo gráfico.

Como discutido na IEEE International Conference Circuitos de Estado Sólido , Siers Intel engenheiro Scott anunciou que haverá quatro diferentes modelos de matrizes Ivy Bridge. Além disso, Ivy Bridge irá transportar até 1,4 bilhões de transistores que decorrerá ao longo de uma área de 160 mm 2, que é cerca de 26 por cento menor do que a 216 milímetros comparável 2 morrem Sandy Bridge com 1,16 bilhões de transistores. Ivy Bridge é construído em 22 nm, que é o "carrapato" processo de Tock da Intel Tick Modelo .

omar um olhar mais atento disposição da Ponte Ivy die estimado, o layout é similar no projeto atual geração Sandy Bridge. A matriz é composta por três seções gerais, 1), 2 núcleos de CPU) Agente de Sistema e 3) núcleo gráfico.