kokas

GF Ouro

- Entrou

- Set 27, 2006

- Mensagens

- 40,723

- Gostos Recebidos

- 3

Minúsculos e incrivelmente rápidos, os microchips semicondutores operam nas fronteiras da física e são feitos do mesmo material que as crianças usam para brincarem na praia: areia.

Iniciou-se assim uma epopeia que nos leva pelo mundo do desconhecido, que regula a vida moderna das sociedades. Nasce com areia, cresce microchip e torna-se processador. Hoje deixamos a segunda parte de uma história que conta muito de como o mundo dos microchips evoluiu e continua a evoluir.

Iniciou-se assim uma epopeia que nos leva pelo mundo do desconhecido, que regula a vida moderna das sociedades. Nasce com areia, cresce microchip e torna-se processador. Hoje deixamos a segunda parte de uma história que conta muito de como o mundo dos microchips evoluiu e continua a evoluir.

Microchip – Trabalho preciso

Estas são as especialidades da litografia. Essencialmente, este é o mesmo procedimento usado há muitos anos para capturar imagens a preto e branco com celuloide ou, de uma forma mais simples, os rolos fotográficos usados antes da era digital.

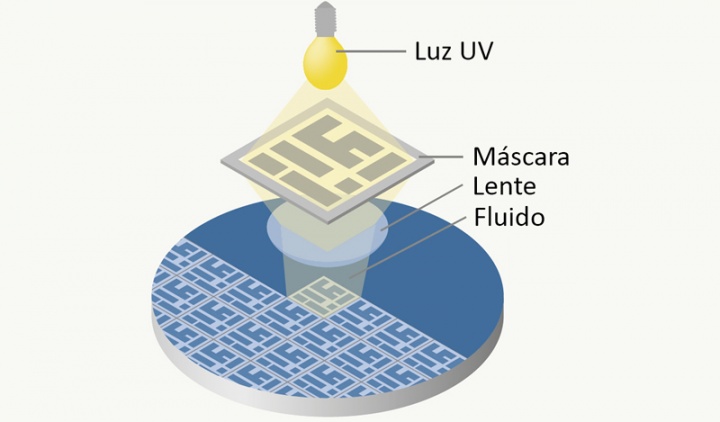

Um sistema ótico direciona a luz para um modelo de uma máscara parcialmente fotossensível. Nos locais onde essa máscara é fotossensível, a luz passa para uma lente que reduz o tamanho do modelo.

A luz, atinge o waffer depois de este ter sido “banhado” com uma laca foto resistente. Neste processo a estrutura química da laca é alterada. Por fim, um produto químico faz com que as áreas alteradas e expostas à luz se desintegrem.

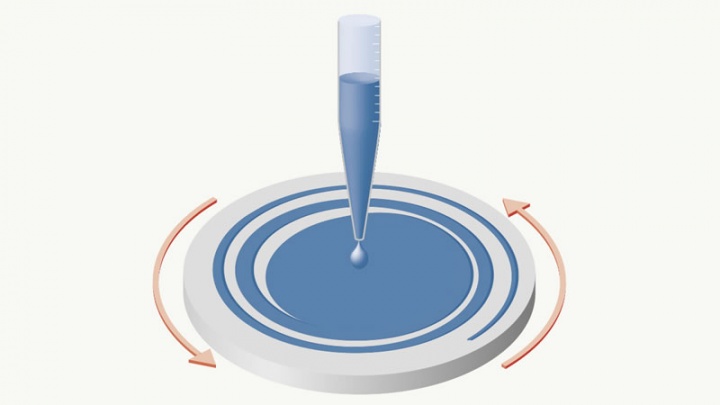

“Spincoating” produz uma camada fina (1 a 2 μm) de laca foto resistente a velocidades entre 3000 a 6000 rotações por minuto.

Um sistema ótico direciona a luz para um modelo de uma máscara parcialmente fotossensível. Nos locais onde essa máscara é fotossensível, a luz passa para uma lente que reduz o tamanho do modelo.

A luz, atinge o waffer depois de este ter sido “banhado” com uma laca foto resistente. Neste processo a estrutura química da laca é alterada. Por fim, um produto químico faz com que as áreas alteradas e expostas à luz se desintegrem.

“Spincoating” produz uma camada fina (1 a 2 μm) de laca foto resistente a velocidades entre 3000 a 6000 rotações por minuto.

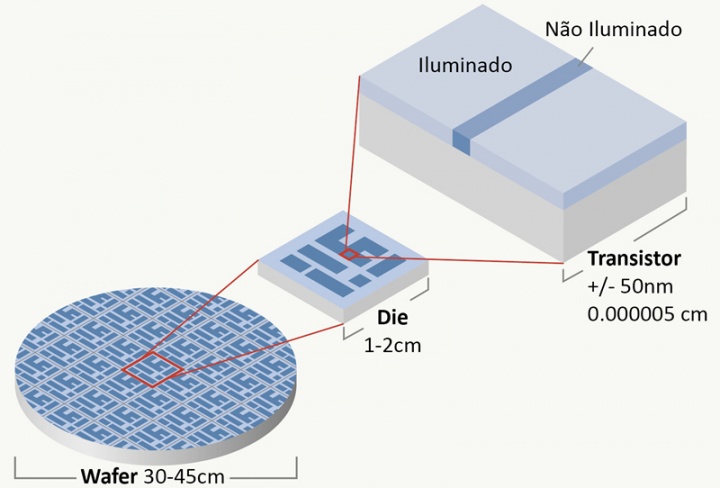

A luz UV é transmitida campo a campo para o silício. Este transmite as estruturas de uma máscara reduzida.

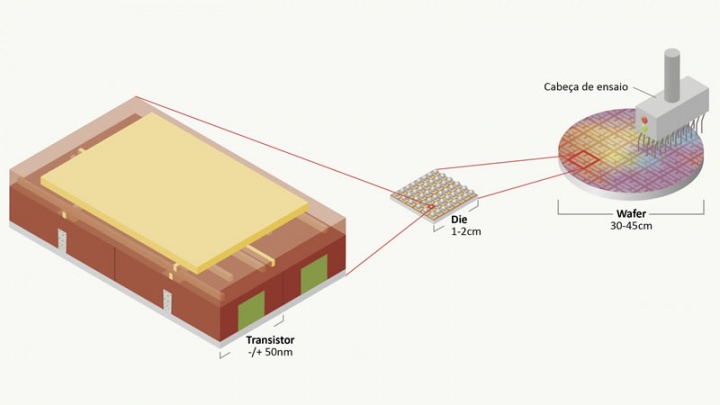

Centenas de “dies” são produzidos num wafer. Cada “die” irá conter mais tarde, muitos mil milhões de transístores. A luz UV altera quimicamente a foto resistência para que o produto químico remova apenas as áreas expostas.

Área Bombardeada

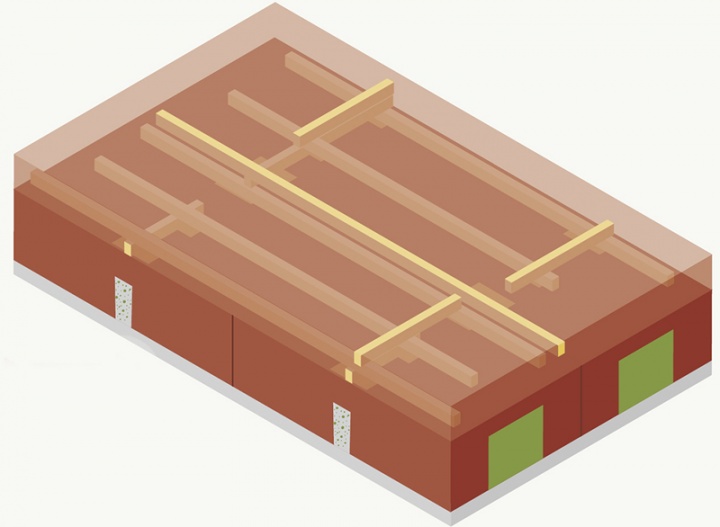

Diretamente no fundo do wafer que se encontra ainda a nu, são colocados os transístores. Os diversos níveis de fiação seguem depois e, por fim, são colocadas as conexões exteriores. Para concluir tudo isto, são necessárias várias centenas de etapas.

Neste artigo, apenas nos vamos concentrar nas etapas mais importantes e interessantes. Além disso, o nosso gráfico, ignora igualmente alguns subpassos para que haja uma melhor clareza. Neste artigo só vamos demonstrar o processo e técnicas mais usadas.

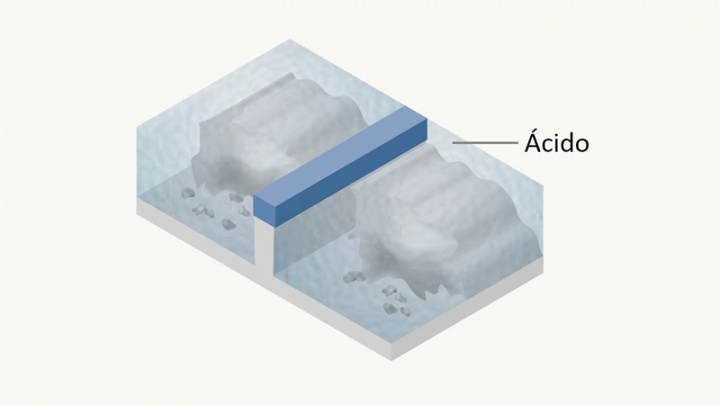

Etching: Remoção do material com acido por gravuraNeste artigo, apenas nos vamos concentrar nas etapas mais importantes e interessantes. Além disso, o nosso gráfico, ignora igualmente alguns subpassos para que haja uma melhor clareza. Neste artigo só vamos demonstrar o processo e técnicas mais usadas.

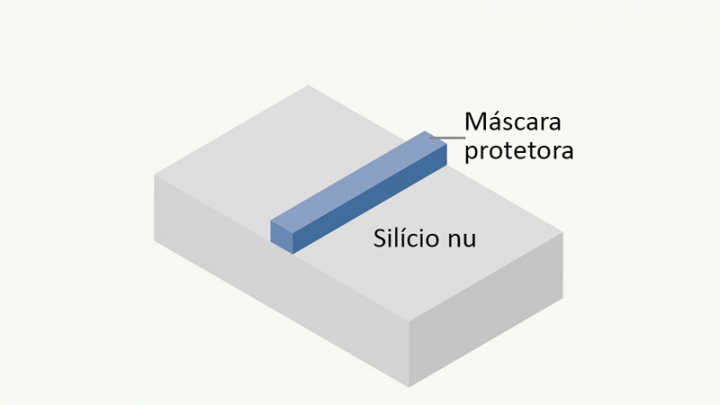

Estruturas tridimensionais de um transístor FinFET são criadas pela remoção de material.

O ácido fluorídrico remove o silício nas áreas desprotegidas, algo que depende sempre do tempo de exposição.

A corrente irá fluir mais tarde, através do transístor quase formado.

As propriedades semicondutoras do material podem ser alteradas com o calor ou com o bombardeamento de átomos exóticos. O uso do calor no método de doping é o mais dispendioso de todos e raramente é usado, visto que implica a utilização de barreiras protetoras em plasma, para que o calor não se disperse pelo silício, danificando o mesmo.

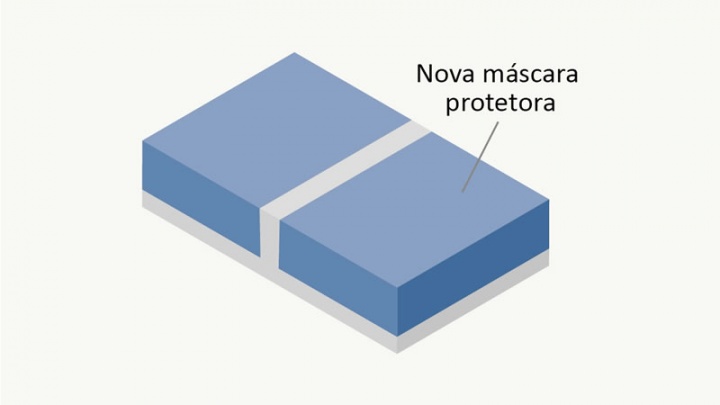

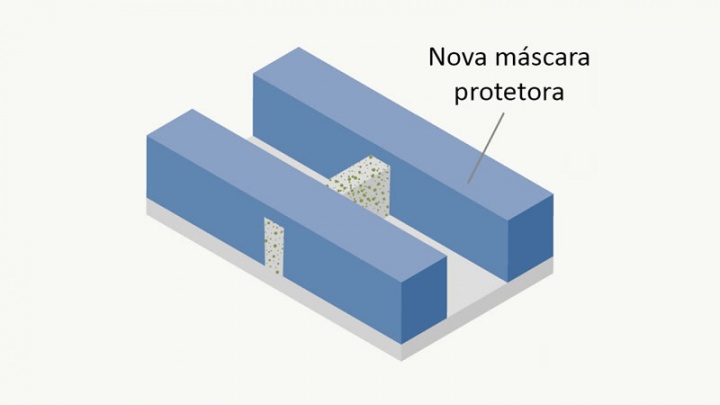

O uso do bombardeamento de átomos exóticos é atualmente o mais vantajoso se dividirmos o TCO (Total Cost of Ownership) pela performance. Neste processo e depois de aplicada uma nova máscara protetora, os átomos exóticos, como o boro, o arsénio e o fósforo, são literalmente bombardeados para as áreas específicas do silício. Como eles têm um número diferente de eletrões do que o silício, a concentração total dos átomos é alterada nas regiões “dopadas”.

Medido pelo número de átomos do Si, poucas impurezas são suficientes para os efeitos desejados. Uma proporção de 1 a 1000 já seria uma “dopagem” extremamente alta. Para alguns componentes, já é suficiente 1 átomo por mil milhões.

Os semicondutores desenvolvem a sua magia nas transições de materiais.

O wafer é bombardeado durante o doping com átomos de boro, fósforo e arsénico, que são depositados na rede cristalina.

Após um múltiplo doping, as três zonas mais importantes do FinFET, já são reconhecíveis, mas ainda faltam várias camadas auxiliares.

Um pouco de malabarismo com detalhes de dissuasão no fabrico desta bolacha de silício extremamente pura revela, que os fabricantes de semicondutores operam nos limites da física.

Um cristal de silício consiste em exatamente 5*1022 átomos por cm³. Embora isto pareça muito, um recorte de um transístor, com a forma de um cubo, num processo de fabrico de 14 nm, consiste em apenas 300 mil átomos. Mesmo com uma dopagem pesada de 1:10000, apenas algumas dúzias de átomos exóticos estarão nesse mesmo cubo. Variações mínimas no fabrico, alteram drasticamente as propriedades do material. Isso é ainda mais problemático, porque tanto o doping como a gravura ou a estrutura das camadas, necessitam sempre de serem confecionadas em toda a superfície de um wafer por camadas.

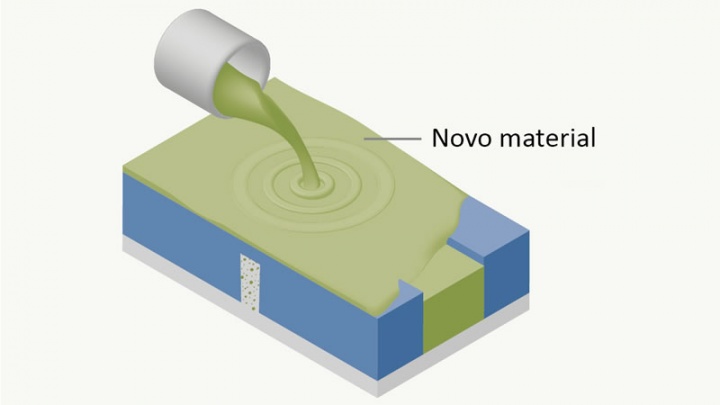

Lift-off: Aplicação de novas camadas com reprodução de cristais, deposição de vapor ou galvanização.

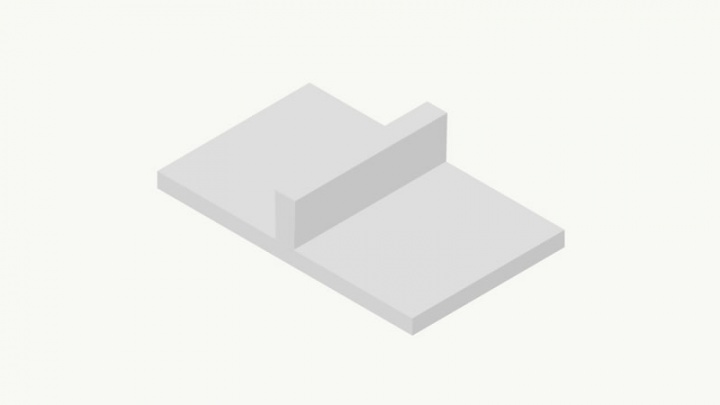

Para criar um portão, é necessário que se criem primeiro as paredes de fixação. Estas novas camadas podem ser aplicadas por epitaxia (crescimento de cristais), deposição de vapor ou galvanização.

As áreas desprotegidas são preenchidas com um novo material condutor.

As mascaras protetoras são novamente retiradas com o processo de doping e assim sucessivamente, camada após camada.

Viver com distorções

Infelizmente, as distorções não se aplicam nas leis da física e aos consequentes limites da ótica. Mesmo a luz ultravioleta de lasers modernos a gás (ArF Excimer Laser), ainda possui um comprimento de onda de 193 nm. Esse é um múltiplo das estruturas mais pequenas que precisam de ser expostas.

De uma forma bastante concreta, isto significa que a resolução de um sistema ótico não é suficiente para uma imagem nítida nessas estruturas. Este, por sua vez, cria padrões de interferência e difração. Este problema é abordado com inúmeros truques, como a correção de proximidade ótica (Optical Proximity Correction), máscaras para mudanças de fase (Phase Shift), exposição múltipla e litografia de imersão.

No último, um líquido enche o espaço entre a lente e a laca que, com o seu maior índice de refração, melhora a resolução ótica. A exposição múltipla com máscaras diferentes cria estruturas na laca, que são mais finas do que aquelas que o laser poderia criar com uma única máscara.

Para compensar os efeitos de difração, as estruturas das máscaras são antecipadamente distorcidas com simulações no computador. Por várias razões técnicas e mecânicas, em particular, é impossível gravar um wafer inteiro de uma só vez. As gravações (8b.jpg) ocorrem em etapas parciais, na qual, somente uma pequena área em cada etapa é exposta aos raios ultravioleta. Um sistema razoavelmente avançado e atualizado para estas gravações é produzido pela empresa do ASML. O ASML Twinscan NXT 1980Di necessita de apenas 15 segundos para gravar 96 campos num wafer de 300 mm. Sem exposições (gravações) múltiplas, ele cria 250 wafers por hora.

O próximo salto tecnológico nesta área seria a litografia ultravioleta extrema (EUV) com comprimentos de onda tão curtos que as interferências já não seriam importantes. No entanto, os fabricantes destas tecnologias, estão literalmente, a atrasar a introdução das mesmas. Isto acontece porque estas empresas se vêem com enormes problemas para reduzir ainda mais o processo de fabrico. Entretanto, o custo destes pequenos saltos tecnológicos dispara para valores nunca vistos. Outra contrapartida é a dificuldade no minério de materiais para lentes e revestimentos que tenham propriedades óticas suficientemente boas para EUV.

Os executoresDe uma forma bastante concreta, isto significa que a resolução de um sistema ótico não é suficiente para uma imagem nítida nessas estruturas. Este, por sua vez, cria padrões de interferência e difração. Este problema é abordado com inúmeros truques, como a correção de proximidade ótica (Optical Proximity Correction), máscaras para mudanças de fase (Phase Shift), exposição múltipla e litografia de imersão.

No último, um líquido enche o espaço entre a lente e a laca que, com o seu maior índice de refração, melhora a resolução ótica. A exposição múltipla com máscaras diferentes cria estruturas na laca, que são mais finas do que aquelas que o laser poderia criar com uma única máscara.

Para compensar os efeitos de difração, as estruturas das máscaras são antecipadamente distorcidas com simulações no computador. Por várias razões técnicas e mecânicas, em particular, é impossível gravar um wafer inteiro de uma só vez. As gravações (8b.jpg) ocorrem em etapas parciais, na qual, somente uma pequena área em cada etapa é exposta aos raios ultravioleta. Um sistema razoavelmente avançado e atualizado para estas gravações é produzido pela empresa do ASML. O ASML Twinscan NXT 1980Di necessita de apenas 15 segundos para gravar 96 campos num wafer de 300 mm. Sem exposições (gravações) múltiplas, ele cria 250 wafers por hora.

O próximo salto tecnológico nesta área seria a litografia ultravioleta extrema (EUV) com comprimentos de onda tão curtos que as interferências já não seriam importantes. No entanto, os fabricantes destas tecnologias, estão literalmente, a atrasar a introdução das mesmas. Isto acontece porque estas empresas se vêem com enormes problemas para reduzir ainda mais o processo de fabrico. Entretanto, o custo destes pequenos saltos tecnológicos dispara para valores nunca vistos. Outra contrapartida é a dificuldade no minério de materiais para lentes e revestimentos que tenham propriedades óticas suficientemente boas para EUV.

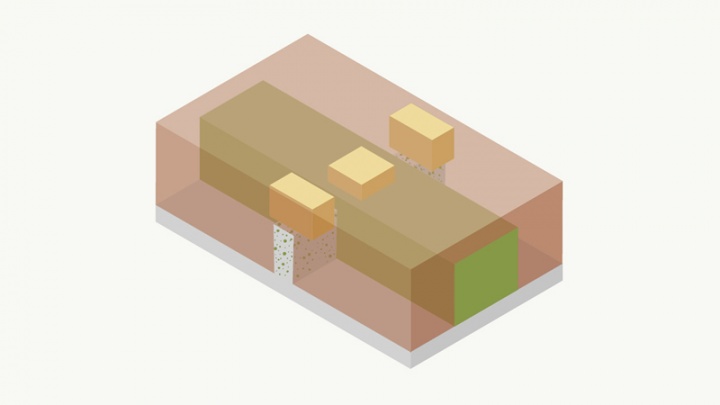

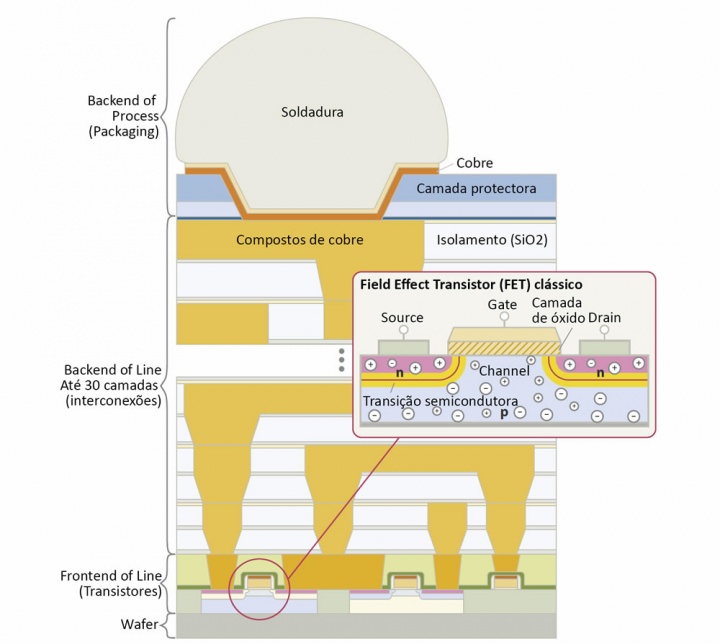

Depois de dezenas de ciclos de corrosão, acumulação e doping com máscaras de litografia sempre novas, os transístores individuais estão finalmente concluídos, mas ainda não estão em comunicação uns com os outros.

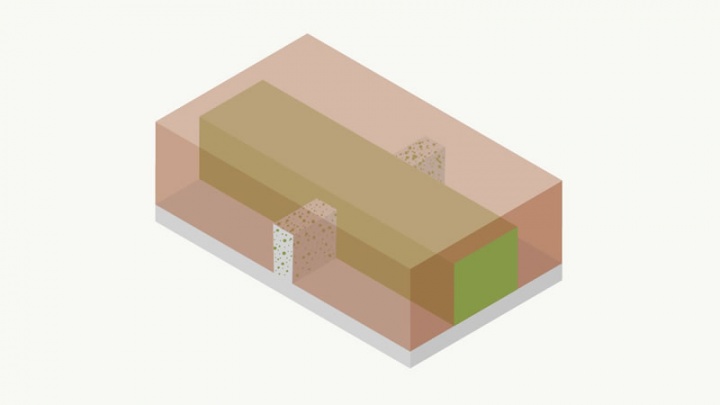

A segunda parte da linha de produção, o backend de linha (Backend of Line), trata da interconexão dos transístores individuais. O fabrico de até 30 camadas de interconexões é semelhante à dos transístores. Em primeiro lugar, é instalada uma camada isolante sobre todo o wafer.

A segunda parte da linha de produção, o backend de linha (Backend of Line), trata da interconexão dos transístores individuais. O fabrico de até 30 camadas de interconexões é semelhante à dos transístores. Em primeiro lugar, é instalada uma camada isolante sobre todo o wafer.

De seguida é usado o método de cauterização (etch) com dióxido de silício. Este método serve, literalmente, para gravar buracos e desenhar trincheiras para pistas onde quer que os circuitos subjacentes sejam interligados.

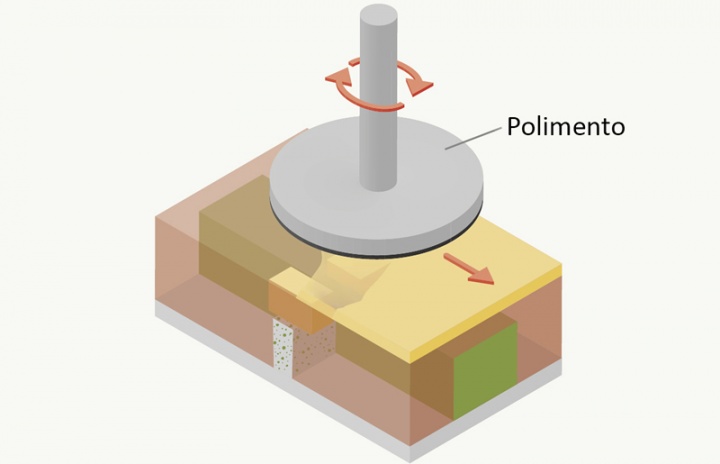

Então, a bolacha de silício é imersa num banho de sulfato de cobre. Uma tensão elétrica entre o wafer e o líquido desencadeia processos eletroquímicos (galvanoplastia).

Estes depositam uma camada de cobre sobre o wafer, que é imediatamente removida por uma lixa até a camada isoladora.

Esta lixa, por fim, termina somente a sua etapa, nas depressões anteriormente escavadas ou, mais precisamente, quando somente os buracos cobertos com cobre estão a vista.

De seguida, o ciclo começa de novo.

À medida que a distância para os transístores aumenta, a largura das estruturas aumenta cada vez mais. Isto faz com que a sua secção transversal aumente também e, assim, reduza a resistência elétrica nas pistas dos condutores.

No topo dos wafers podem ser encontradas as soldaduras. Estas são pequenas bolas, que mais tarde conectam o chip ao mundo exterior. Ainda nas bolachas de silício, o funcionamento dos chips é testado e estes são selecionados.

De seguida, uma serra circular corta a bolacha de silício ao longo das suas ruas. Estas ruas são chamadas de “Die Streets” e são tão grossas quanto um cabelo humano, sendo a lâmina da serra ainda mais fina. Essa gira a uns incríveis 60 000 rpm. Mas ainda antes do processo de corte, uma película especial é colada sobre o wafer, de forma a evitar danos e para que estes não voem durante o corte.

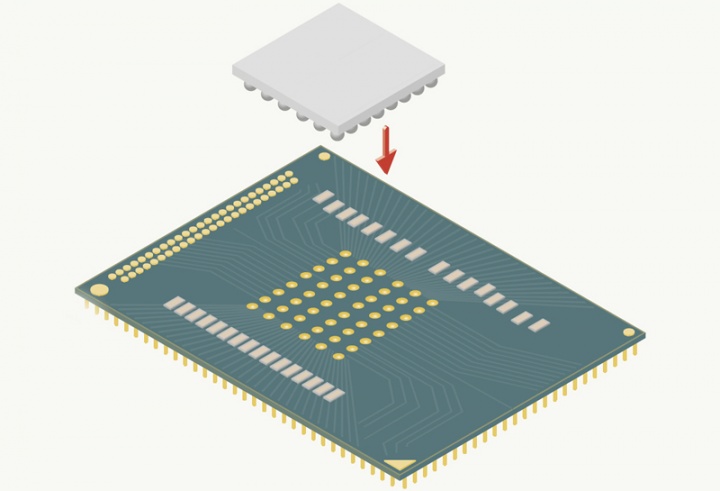

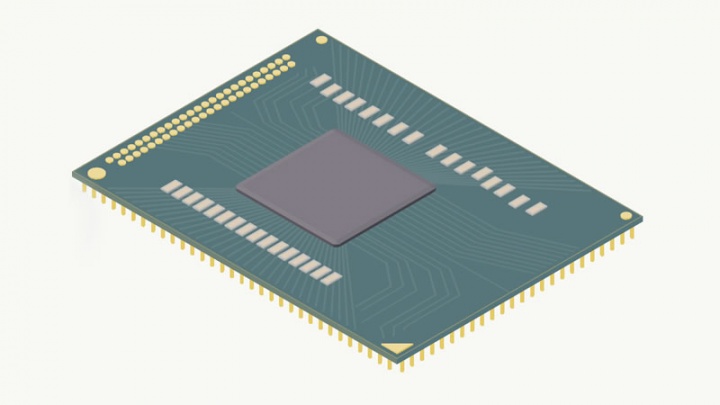

Dependendo do uso pretendido, o chip ainda recebe uma carcaça de proteção ou, pelo menos, uma base chamada de Die-Carrier.

No método de flip-chip, este é soldado de cabeça para baixo no Die-Carrier. Neste caso, o lado inferior usado na produção da bolacha de silício torna-se o lado superior do processador. Este método serve para uma melhor dissipação de calor e é o método usado por todas as empresas que produzem microchips de alta performance.

Enquanto o dissipador de calor nos chips para computadores portáteis fica diretamente em cima do Die, os processadores para computadores convencionais recebem uma tampa de estanho por cima do mesmo. Este é chamado de Heatspreader e protege o fragmento frágil e espalha o calor.

Estrutura das camadas dum processador

Na parte inferior do silício encontram-se os transístores individuais. Seguem-se muitas camadas de minúsculos fios de cobre individuais que são interligados aos diversos transístores. Quanto mais próximo da soldadura, mais grossos são esses fios.

Este é um segundo artigo que aprofundar conceitos. Iremos ainda voltar a pormenorizar outras áreas deste mundo dos microchips.